|      |                   | -  |   |

|------|-------------------|----|---|

| DOCL | $\mathbf{\Omega}$ | 7  | 3 |

|      | •                 | 1. |   |

# **SB8010**

Z80 CPU CARD

REFERENCE MANUAL

APPLICABILITY D

REVISION DATE 12/20/83

#### 1.0 INTRODUCTION

The Micro/sys SB8010 is a highly versatile card comprised of a Z-80 microprocessor, 4 general purpose 28 pin sockets for byte-wide ROM and/or RAM chips, a Z-80 CTC counter-timer, and a serial I/O port (USART) using Intel's 8251. A bootstrap option is provided for loading an operating system into main memory using an on-board PROM.

On-board memory can be mapped in various ways to match the memory chips selected. The mapping options are accomplished using a PROM. The User may install his own PROM if a different mapping is desired. However, the six mappings provided should satisfy most users.

The serial I/O chip uses the counter-timer chip as the clock source for both receiver and transmitter to that baud rate is programmable by software. RS-232 buffers are provided for all the serial outputs and inputs. In an interrupt driven system, the serial chip (8251) uses the CTC as an interrupt controller, enabling the serial chip (8085 peripheral) to benefit from the sophisticated 2-80 interrupt scheme.

The CTC can also be used as an interrupt controller for external events as well as a general purpose counter and/or timer.

Detailed card operation is discussed in section 2. Section 3 explains all user options. Section 4 provides register addresses of all the on-board I/O functions as well as rough guidelines to several modes of operation.

Appendix B contains a Zilog Z-80 data sheet with a mnemonics summary. Detailed Z-80 programming information is not provided as this is commonly available elsewhere. Appendix C and D contain 8251 and CTC data sheets and/or programming information. Refer to these appendices for I/O programming guidelines while obtaining specific register addresses from Section 4. Appendix E and F contain the data programmed into the memory decoder PROM and the I/O decoder PROM. Finally, appendix G contains the PAL (Programmable Array Logic) equations.

### TABLE OF CONTENTS

| 1.0 INTRODUCTIO | ION | CT' | טסט | INT | .0 | 1 |

|-----------------|-----|-----|-----|-----|----|---|

|-----------------|-----|-----|-----|-----|----|---|

#### 2.0 THEORY OF OPERATION

- 2.1 BUFFERS

- 2.2 RESET CIRCUIT

- 2.3 MAIN LOGIC

- 2.4 on-board MEMORY

- 2.5 BOOT CIRCUIT

- 2.6 on-board I/0

- 2.7 INTERRUPT SYSTEM

#### 3.0 CONFIGURATION AND OPTIONS

- 3.1 EXTERNAL CONNECTORS

- 3.2 ON-BOARD MEMORY

- 3.2.1 RESTRICTIONS

- 3.2.2 CONFIGURING THE MEMORY SOCKETS

- 3.2.3 ENABLING THE SOCKETS

- 3.2.4 MEMORY MAP AND BOOT OPTION

- 3.3 MEMEX AND ICEXP

- 3.3.1 MEMEX

- 3.3.2 IOEXP

- 3.4 ON-BOARD I/O

- 3.4.1 OUTPUT CONNECTORS

- 3.4.2 I/O CONFIGURATIONS

- 3.4.2.1 USING THE SERIAL CHIP

- 3.4.2.2 USING THE CTC TO CONTROL EXTERNAL INTERRUPTS

### 4.0 PROGRAMMING

- 4.1 I/O ADDRESSES

- 4.1.1 THE SERIAL CHIP ADDRESSES

- 4.1.2 THE CTC CHIP ADDRESSES

- 4.2 SERIAL CHIP BAUD RATE PROGRAMMING

- 4.2.1 GUIDELINES FOR BAUD RATE PROGRAMMING

- 4.3 USING THE CTC AS AN INTERRUPT CONTROLLER

- 4.4 RESETTING THE SERIAL CHIP

### APPENDICES

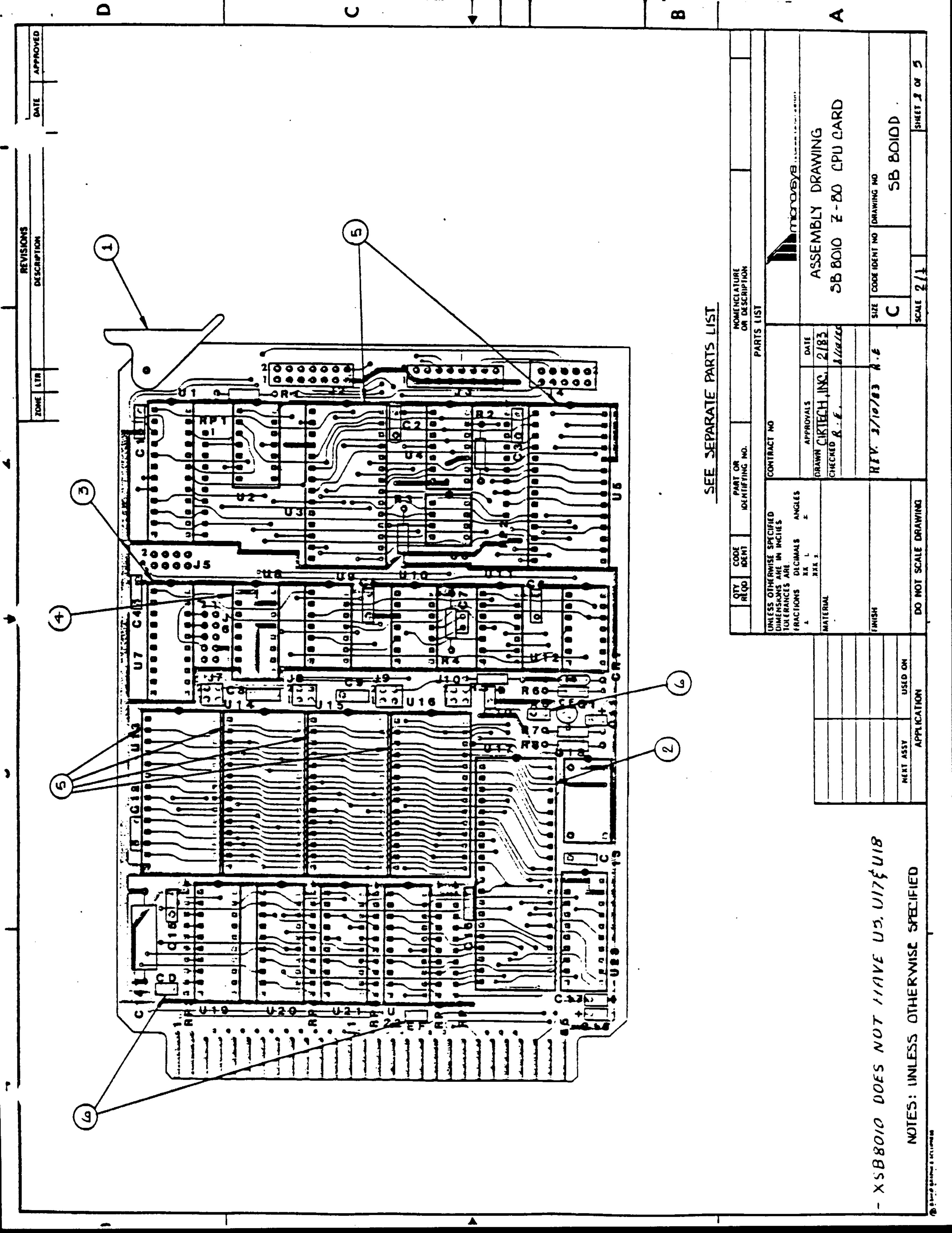

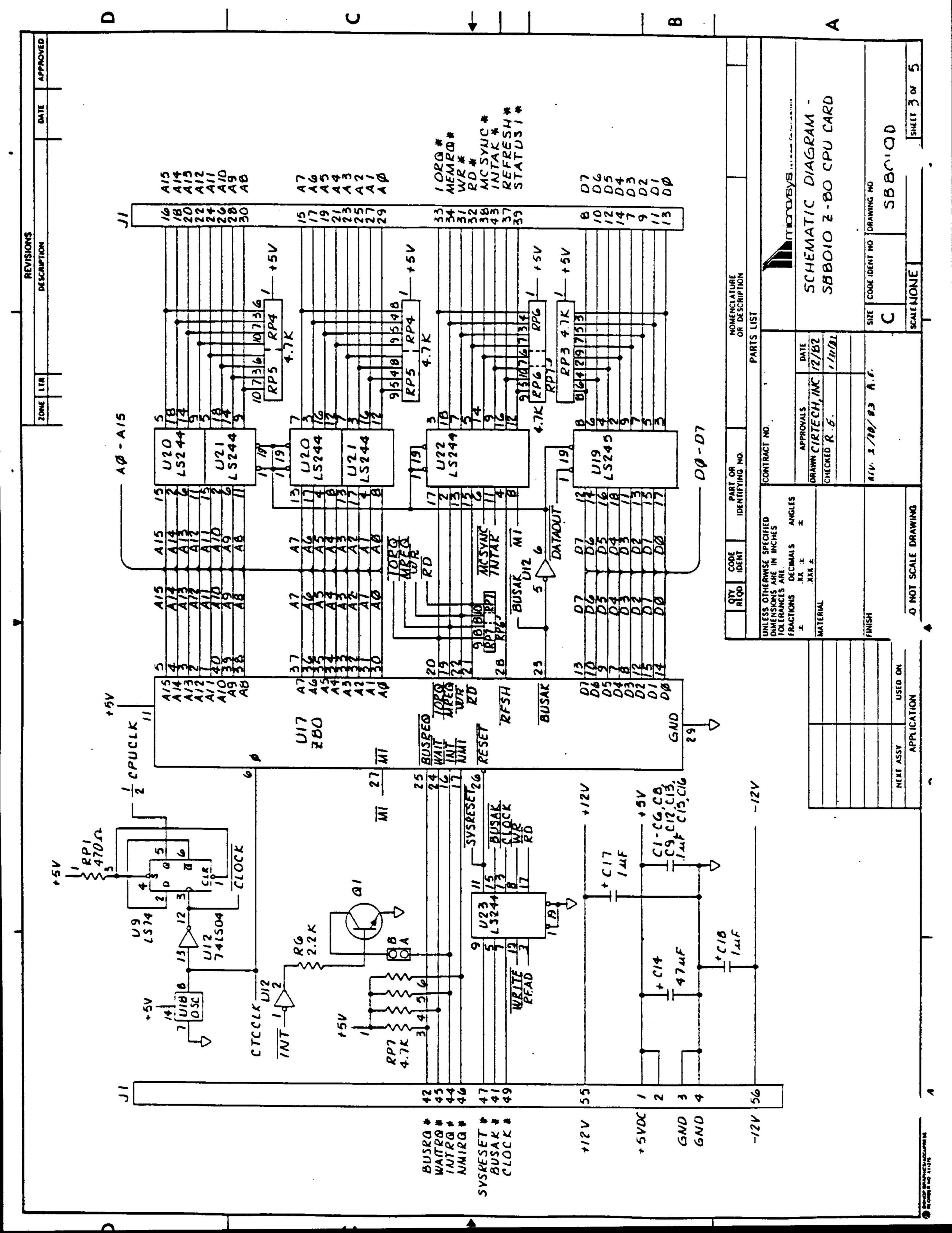

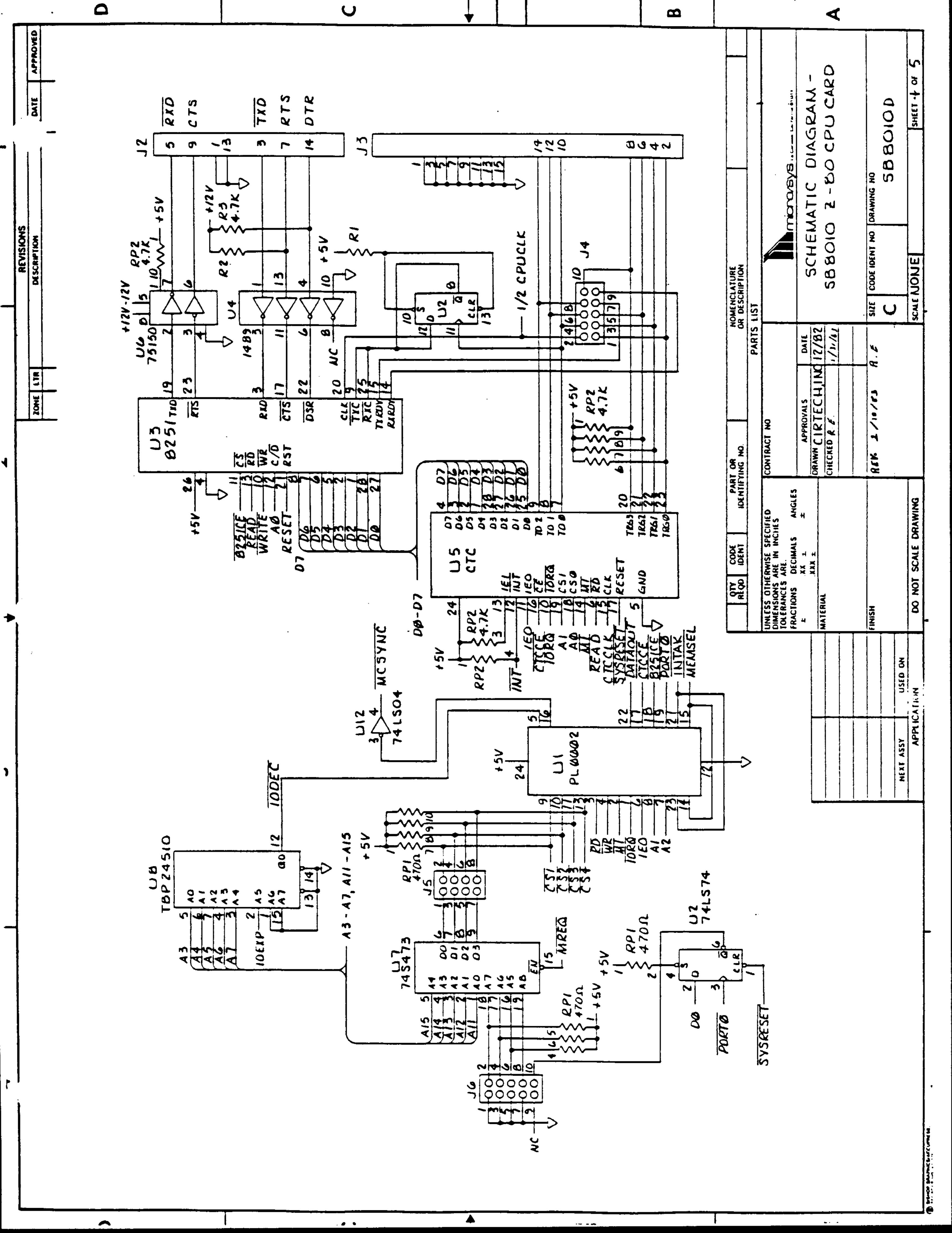

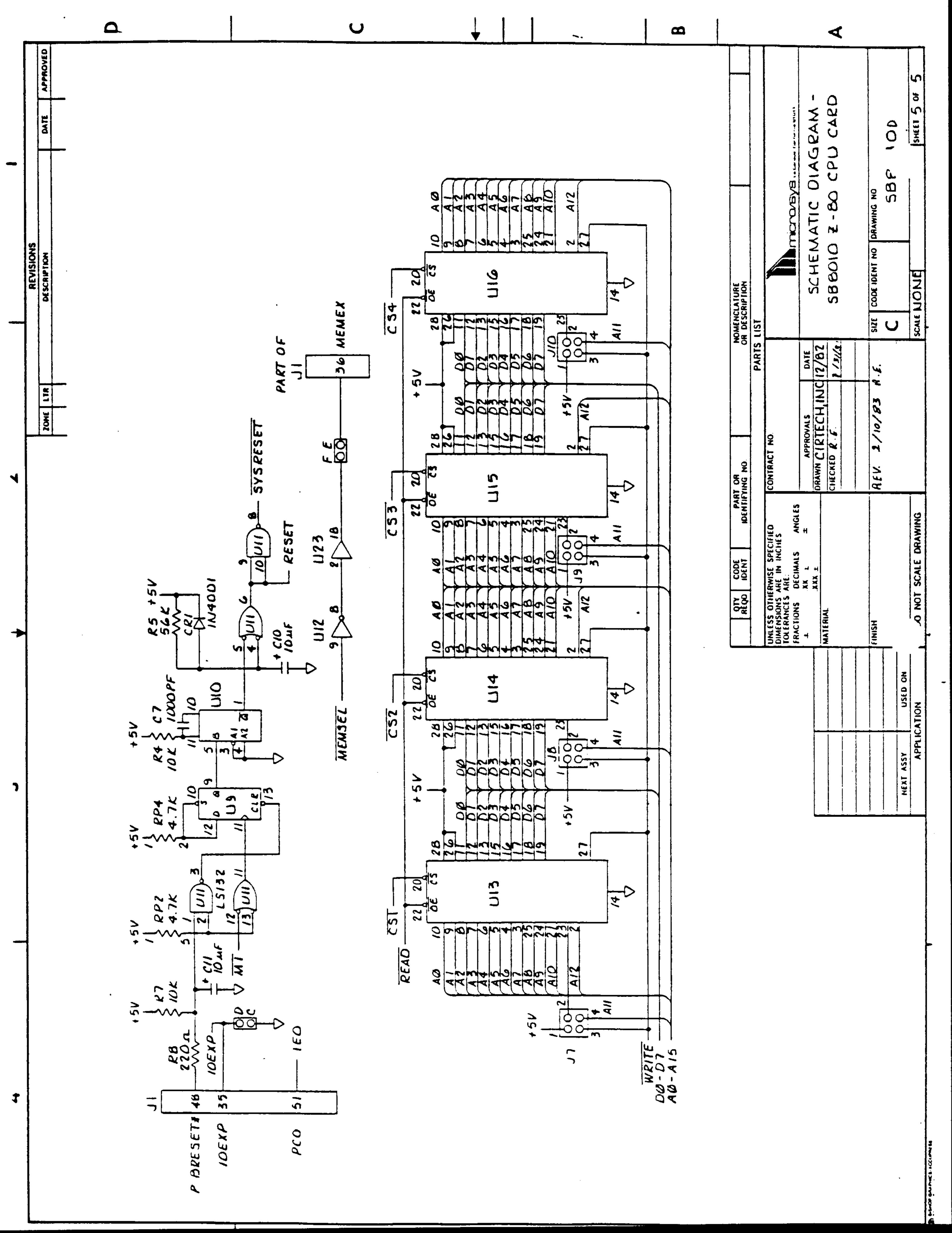

- A ASSEMBLY, SCHEMATICS DIAGRAMS

- B Z-80 DATA SHEET

- C SERIAL CHIP 8251 DATA SHEETS

- D CTC (COUNTER/TIMER CHIP) DATA SHEETS

- E MEMORY DECODER PROM

- F I/O DECODER PROM

- G PAL (PROGRAMMABLE LOGIC ARRAY) EQUATIONS

### 2.0 THEORY OF OPERATION

### 2.1 BUFFERS

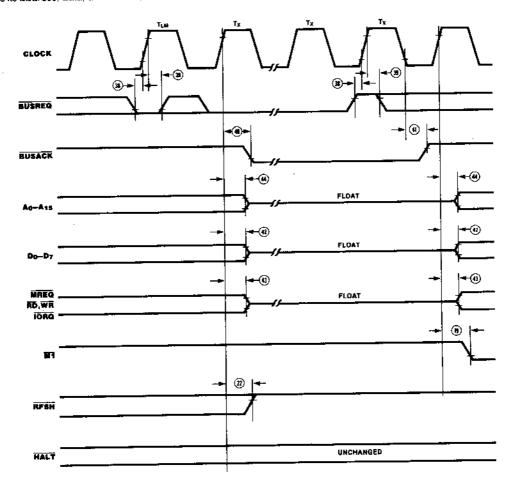

All address lines, data lines and output control lines are buffered to provide sufficient drive to a multi-module system. The address and control buffers are unidirectional, pointing towards the bus. The only time they are turned off (in high impedance state) is during a DMA cycle.

The data buffer is bidirectional. It is pointing out (to the bus) during a write operation or an on-board read. It is pointing in during a read which is not on-board. It is turned off during a DMA cycle.

Four input CPU control lines, namely BUSREQ/, WAIT/, INT/ and NMI/, are driven directly off the bus. These lines are static protected by pull up resistors. The advantage of this arrangement is greater response speeds. This is especially important with the WAITRQ/ signal when operating with dynamic memories.

## 2.2 RESET CIRCUIT

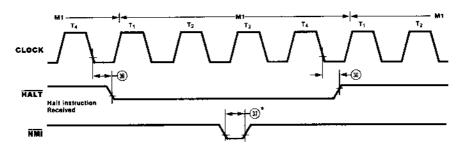

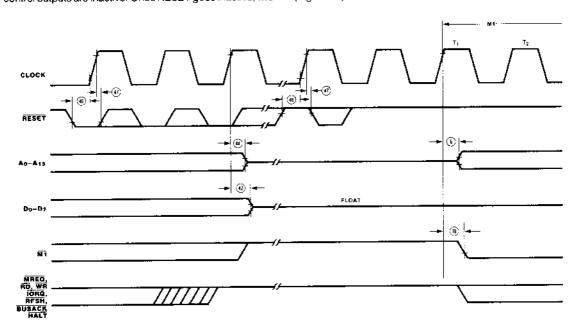

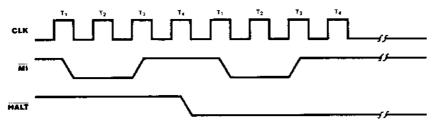

The SB8010 reset circuit provides a reset pulse to the CPU and the SYSRESET/ line on the bus when either the push button reset is activated or power is turned on. The pulse generated is synchronized with the beginning of a fetch cycle and has a fixed duration irrespective of the duration of the push button reset signal. The purpose of this scheme is to avoid the possibility of erasing dynamic memories using CPU refresh. Upon reset the CPU starts fetching instructions from address 0.

### 2.3 MAIN LOGIC

Most of the logic functions on the card are performed using a PAL (Programmable Array Logic) at Ul and 2 PROMS (U8 and U7). The PROMS provide the PAL with decoded address signals for on-board memory and I/O. The PAL, along with CPU control signals and address lines Al and A2, does the following:

- a. Determines direction of the data buffer

- b. Enables the serial I/O port

- c. Enables the timer/counter ship

- d. Enables the boot flip flop

- e. Generates STD bus signals MCSYNC/ and INTAK/

Appendices E and F contain the data programmed into the decoder PROM's. Appendix G contains the PAL equation.

# 2.4 ON-BOARD MEMORY

Four general purpose memory sockets are provided that can be configured to accept ROM/PROM/EPROM and/or RAM chips of sizes 2,4 or 8K bytes. (See restrictions in section 3.2.1). A memory map PROM (U7) enables these chips according to one of 6 different combinations of sizes and mappings selectable via option posts. The memory maps selected all start at address zero. mappings provided will satisfy most users. However, the user may program his own PROM if a different mapping is desired (Up to 8 different mappings can be programmed.). Appendix D contains the data programmed into this PROM. mappings mentioned here may be conditioned with a signal from the boot flip flop (U2 pin 6) if J6 pins 8 and 10 are connected. When this signal is high (pin 19 of U7 is high), a different set of memory map is enabled. These additional maps are used for bootstrapping. See next section.

Whenever on-board memory is accessed, the MEMEX line is activated, disabling off-board memory that occupies the same memory space. Thus a 64 K RAM card can be used as main memory without any conflict with on-board memory. It should be noted, however, that the memory cards that you use should comply with the STD specifications with respect to MEMEX if you wish to use overlapping on-board memory. (A few manufacturers have "forgotten" MEMEX in their design.)

## 2.5 <u>BOOT CIRCUIT</u>

The boot circuit allows a program on disc, cassette, etc. to be loaded into memory. When power is switched on or when a reset pulse is generated, the boot flip flop (U2 pin 6) outputs a high logic level. If J6 pins 8 and 10 are connected, this level is routed to U7 pin 19.

This selects a different set of memory maps at U7 as discussed in the previous section. This memory mapping will enable a PROM at address zero which can be used (in most cases) to boot a program from, say, disc into memory.

Once the program in the boot PROM has been executed, the PROM can be switched off via an I/O operation. (It can also be switched back on with an I/O operation). Two memory map options are provided for booting, both of which are starting at address zero. This again will satisfy most users. If desired, the user may custom program his own memory map PROM, in which case 8 different maps can be programmed.

## 2.6 <u>ON-BOARD I/O</u>

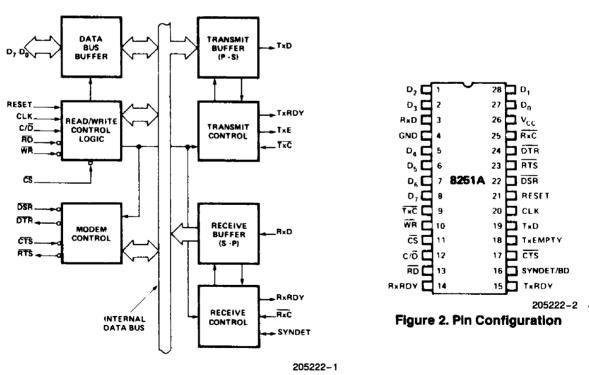

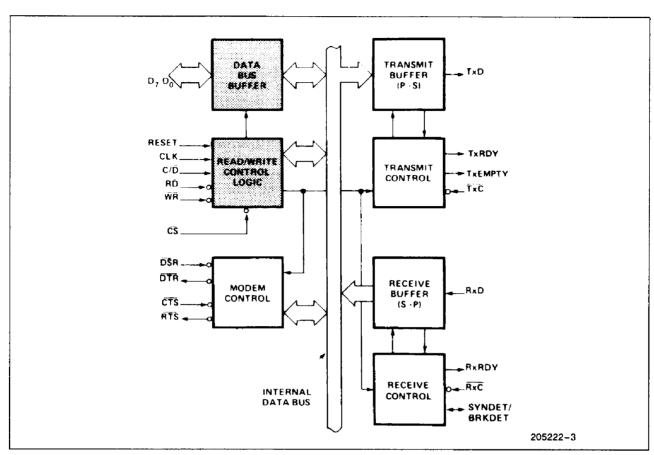

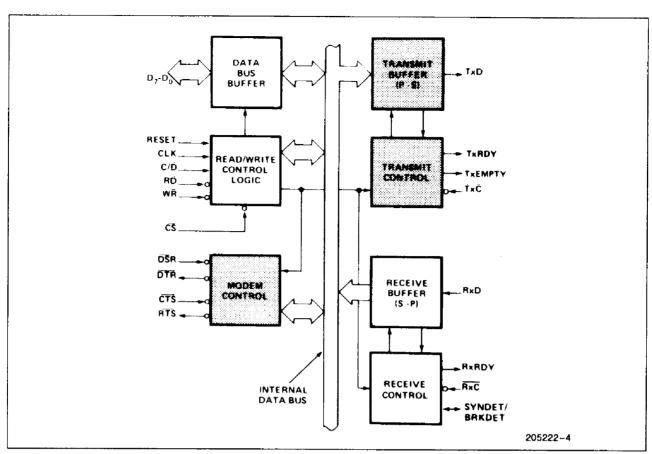

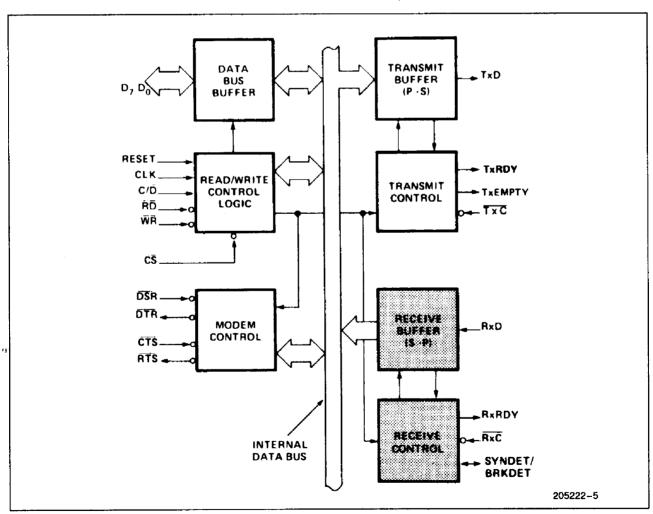

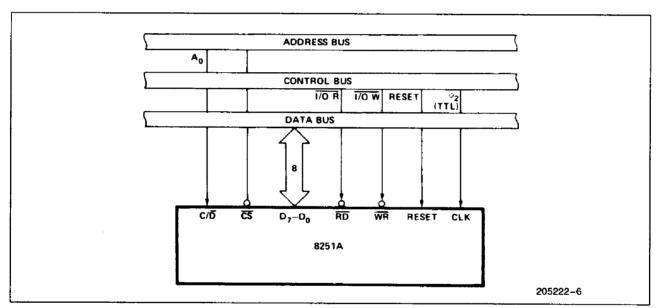

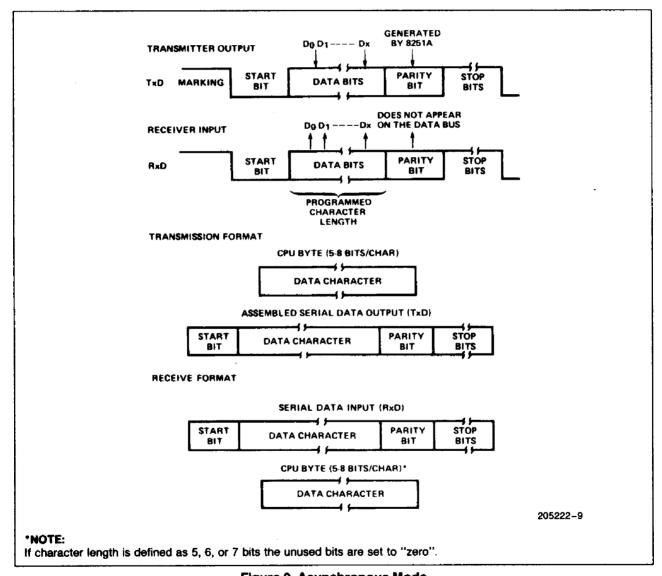

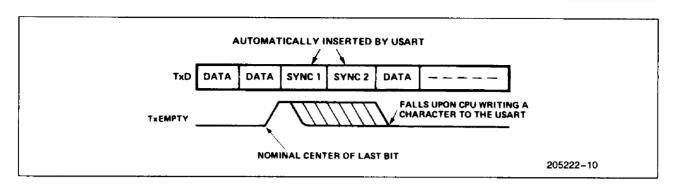

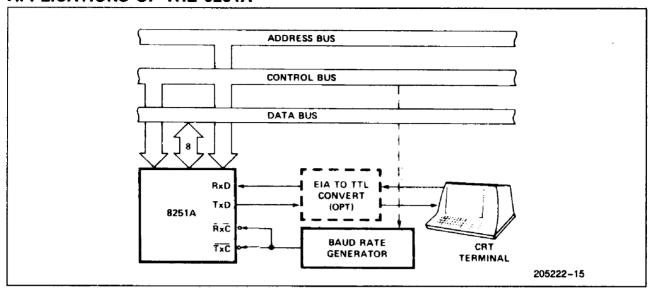

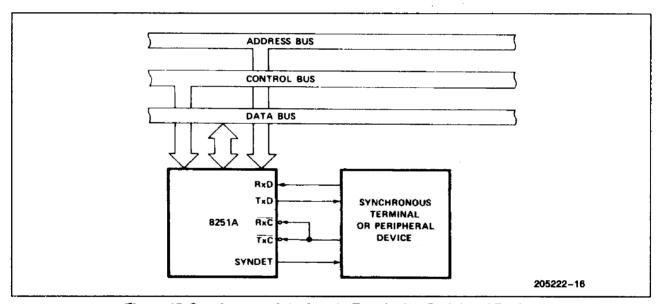

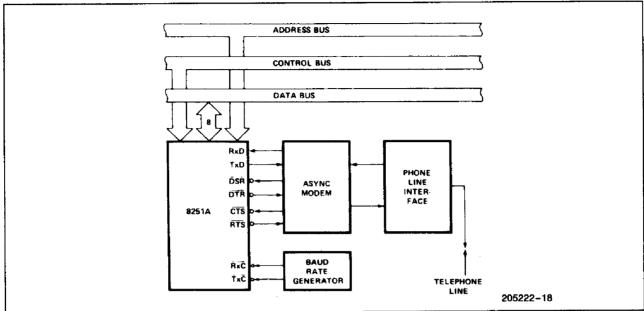

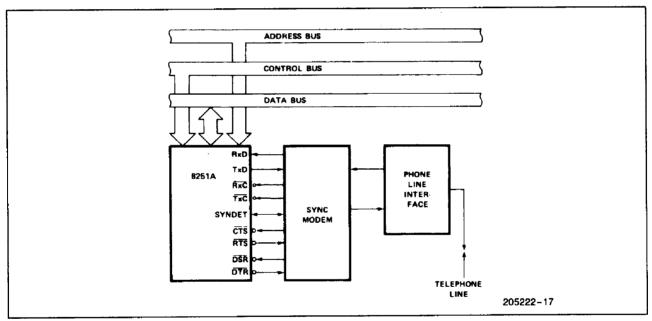

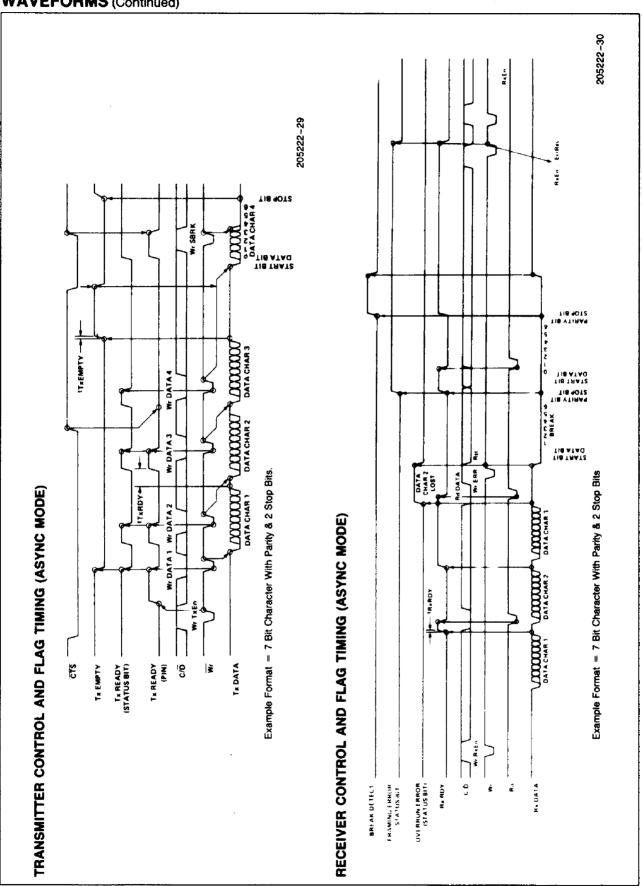

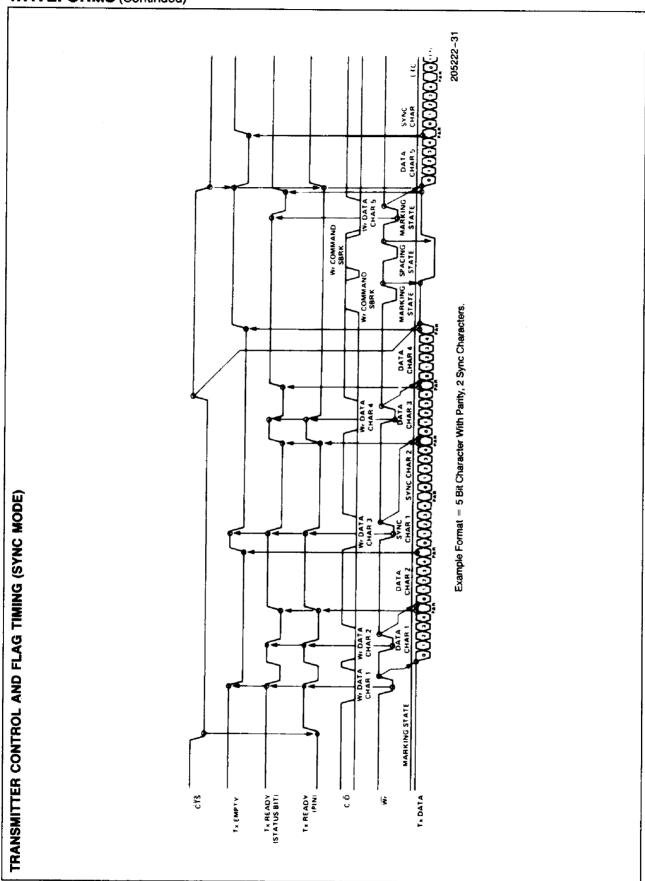

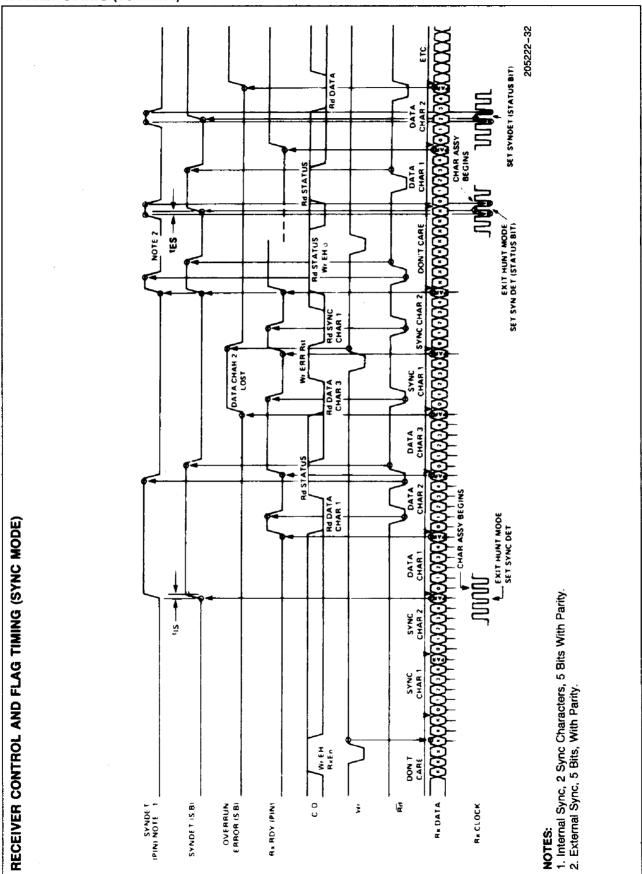

Two LSI chips, the 8251 and Z80-CTC, provide serial I/O and timer/counter functions, respectively. The 8251 is a general purpose, single channel USART capable of being programmed to operate in most serial data transmission techniques presently in use. The SB8010 card supports only asynchronous transmission and reception. Most asynchronous baud rates from 50 to 4800 are programmable. Data and control signals CTS, RTS and DTR are buffered using RS-232 line drivers and receivers. The serial I/O signals are available at connector J2. The pins are arranged so that a standard RS232 "D" type connector can be directly connected to J2 using flat ribbon cable.

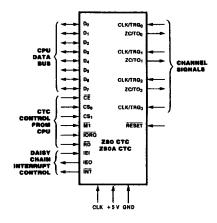

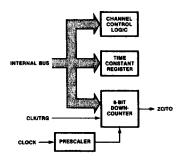

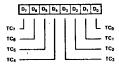

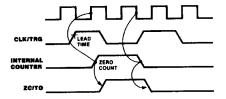

The Z80-CTC is a counter/timer chip having four independent channels, each with a readable 8 bit downcounter and a selectable 16 or 256 prescaler (for timer mode only). Three channels have "zero count" outputs. All channels have clock/trigger inputs that start the timer in the timer mode or decrement the counter in the counter mode. The 4 clock/trigger inputs and the 3 "zero count" outputs are available unbuffered at connector J3.

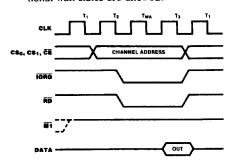

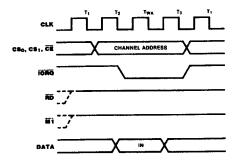

When using the 8251, one channel of the CTC has to be programmed to provide the receive and transmit clocks. The other three channels may be used as general purpose timers or counters. Since the CTC is a Z-80 peripheral, a common use of it is as an interrupt controller (3 channels in this case). This is done by programming a channel to operate in the counter mode with a time constant of 1. If interrupts are enabled, the first pulse at the respective trigger input will generate an interrupt. The 8251, not being a 2-80 peripheral can thus use the CTC to operate as an interrupt driven serial I/O. The CTC is placed at the top of the interrupt priority chain. (Refer to Section 2.7). I/O address decoding is done using a PROM. The card uses 8 I/O addresses starting at address FO HEX. If these I/O addresses interfere with other I/O addresses, the user may program his own PROM. Appendix F contains the data programmed into the I/O decoder PROM.

### 2.7 INTERRUPT SYSTEM

This section will discuss briefly the Z-80 interrupt system and the interrupt management particular to this card. A more thorough Z-80 interrupt description is widely available in manufacturer publications and the unfamiliar user should refer to those.

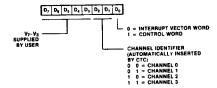

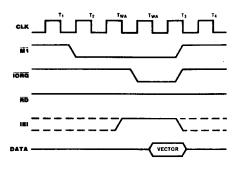

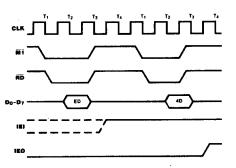

There are three modes of maskable interrupts programmable by software: Mode 0 - the interrupting device places an instruction on the data bus. This is normally a restart instruction which will initiate a call to one of 8 restart locations. Mode 1 - In this mode no vector is placed on the bus and the CPU goes to location 0038H. Mode 2 - In this mode the CPU uses the byte transferred by the peripheral as the lower byte of a pointer directing the CPU to a table of service routine addresses. The high byte of the pointer is furnished by the previously loaded interrupt register. The CPU then jumps to the routine at that address.

There is also one non-maskable interrupt input. Here the CPU performs a restart 0066H.

No interrupt is recognized when BUSREQ/ signal is active.

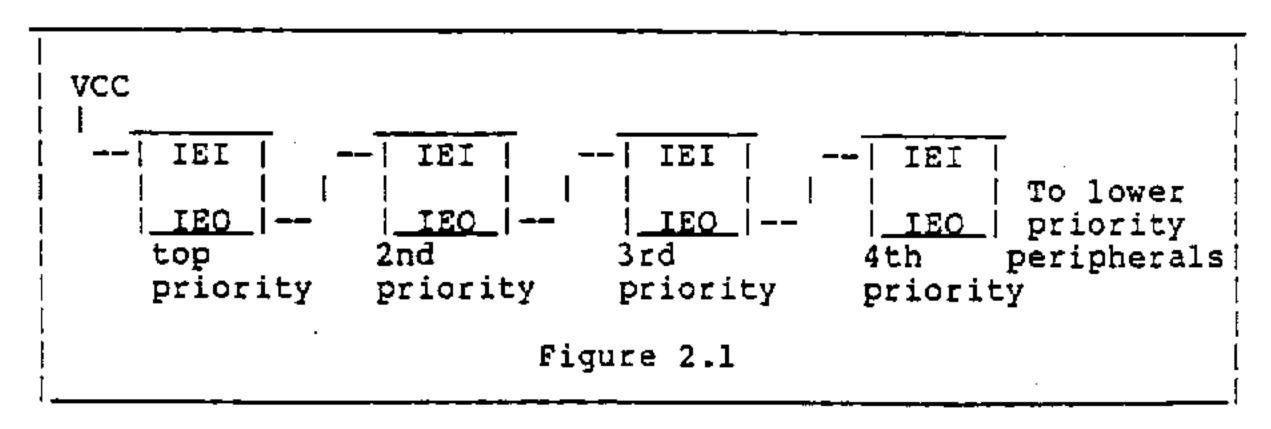

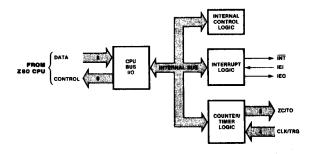

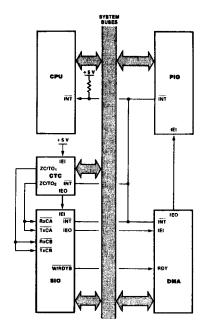

Z-80 peripherals resolve interrupt priority by means of their own logic, unlike 8080/8085 peripherals that require an interrupt controller. Each peripheral has IEI (Interrupt Enable Inable) and IEO (Interrupt Enable Output). These pins are daisy chained by connecting them as shown in figure 2.1.

A device will not request an interrupt if its IEI is low in which case it will also turn its IEO low. It will also turn IEO low when it requests

an interrupt itself. Thus IEO/IEI propagate downwards, disabling all the lower priority interrupts. When servicing the interrupt the CPU automatically disables all other interrupts unless an "enable interrupt" command has been issued in the interrupt service routine (which will enable nesting the interrupts). Upon completion of the service routine an RETI instruction is executed. This instruction is recognized by the interrupting peripheral causing it to turn IEO high again (if no higher priority requests an interrupt at this instance).

As outlined in Section 2.6 the time/counter chip can be used as an interrupt controller to service non A-80 peripherals (e.g., the on-board 8251 and/or external events). If the serial chip is not used, up to four interrupt channels are available, otherwise only three interrupt channels are available. (One channel is used as a baud rate generator for the serial chip.) channel for generating interrupts, the CTC is programmed for the counter mode with interrupts enabled, a value of 1 is loaded as a time constant, and an interrupt vector is loaded. a level changes at the TRG/CLK input, the counter will decrement to zero and issue an interrupt. Channel 0 is the highest priority and channel 3 is the lowest. The IEI pin of the CTC is tied high, thus placing it on top of the priority chain.

## 3.0 <u>CONFIGURATION AND OPTIONS</u>

## 3.1 EXTERNAL CONNECTORS

There are three external connectors - J1, J2, and J3. J1 is the STD bus edge connector. For pinout description refer to STD bus specifications. J2 and J3 are the serial I/O and the timing/counting I/O interface respectively. Tables 3.7 and 3.8 describe J2 and J3 respectively. Table 3.1 provides connector part numbers from ANSLEY as a reference. Similar connectors from different manufacturers may be used.

| TABLE 3.1 | SUGGESTED      | CONNECTORS    |

|-----------|----------------|---------------|

| CONNECTOR | NO. OF<br>PINS | ANSLEY<br>P/N |

| J2        | 14             | 609-1401M     |

| J3        | 16             | 609-1601M     |

### 3.2 <u>ON-BOARD\_MEMORY</u>

### 3.2.1 <u>RESTRICTIONS</u>

On-board 2K, 4K, and 8K memory chips of any kind may be used provided their access time from chip enable or chip select (not output enable!) does not exceed 215ns for a 4MHZ CPU card version or 405ns for a 2.5MHZ CPU card version. Wait states cannot be generated on-board to alleviate this restriction.

## 3.2.2 CONFIGURING THE MEMORY SOCKETS

The memory sockets are 28 pin universal sockets capable of accepting various 24 or 28 pin memory chips. The following chips may be used: Static RAMS and ROM/PROM/EPROM chips of 2K x 8, 4K x 8 and 8K x 8. To configure a socket for a chip, follow the following procedure:

- a. Determine which socket you need to place the chip in by selecting the appropriate memory map to be used. (Refer to Table 3.7).

- b. Determine which option post group corresponds to that socket by using Table 3.2.

| TABLE 3.2 | OPTION POSTS TO<br>SOCKET DESIGNATION |

|-----------|---------------------------------------|

| SOCKET    | CORRESPONDING OPTION POSTS            |

| U13       | J7                                    |

| <br>  U14 | J8                                    |

| <br>  U15 | J9                                    |

| U16       | J10                                   |

c. Use Table 3.3 to determine the connection at the option post from step b.

| TABLE 3.3 CONFIGURATION OF THE OPTION POST (from b) |                      |                     |                     |

|-----------------------------------------------------|----------------------|---------------------|---------------------|

| MEMORY<br>SIZE                                      | !<br> <br>  2KX8<br> | <br> <br>  4KX8<br> | <br> <br>  8KX8<br> |

| RAM                                                 | 3&2                  | 2&4                 | 2&4                 |

| ROM/PROM/<br>EPROM                                  | 1&2                  | <br>  2&4           | 2&4                 |

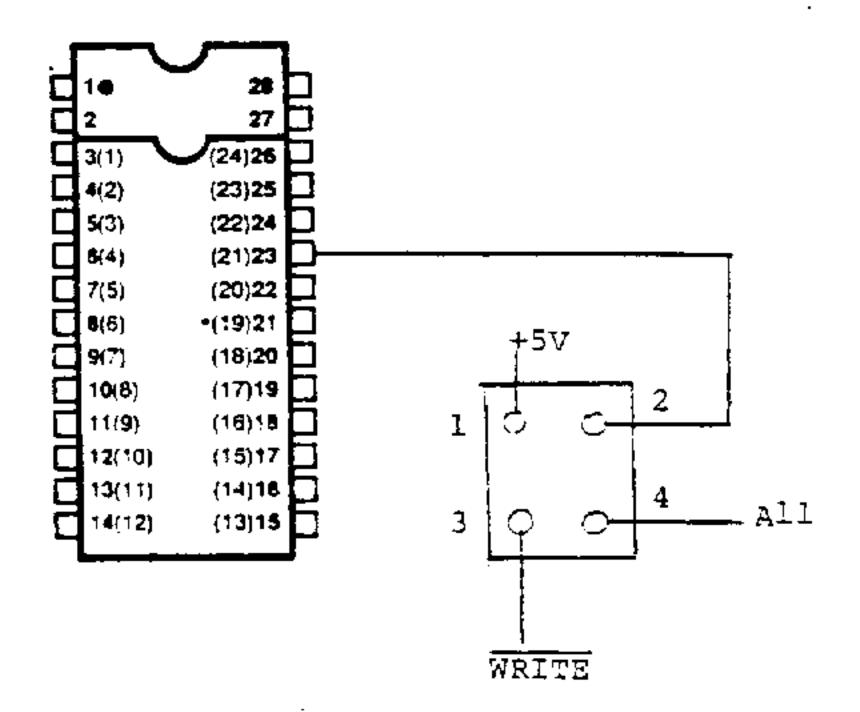

The memory chip is then placed in the lower part of the socket if it is a 24 pin device. For further clarification refer to Figure 3.1

FIG. 3.1 A TYPICAL SOCKET AND ITS CORRESPONDING OPTION POST

SOCKETS: U13,U14,U15,U16

OPTION POSTS: J7,J8,J9,J10

## 3.2.3 <u>ENABLING THE SOCKETS</u>

Each chip can be individually enabled by a connection at J5. With any memory map selection (Table 3.7) the user may select only part of the memory map by not connecting all the jumpers at J5. For example, the user can have an 8K PROM located between 4000H and 6000H-I by selecting map option 7 (Table 3.7) but only enabling U15 by connecting J5 pins 5 and 6. So only at these addresses will there be an on-board access, and external overlapping memory will be masked by MEMEX.

Refer to Table 3.4 to determine connections at J5.

| TABLE 3.4 enabling the memory sockets |                     |  |

|---------------------------------------|---------------------|--|

| TO ENABLE SOCKET:                     | CONNECT<br>J5 PINS: |  |

| U13                                   | 1 & 2               |  |

| U14                                   | 3 & 4               |  |

| U15                                   | 5 & 6               |  |

| Ul6                                   | 7 & 8               |  |

# 3.2.4 MEMORY MAPS AND BOOT OPTION

There are two different sets of memory maps selectable via the boot flip-flop if J6 pins 8 and 10 are connected. If instead, J6 pins 7 and 8 are connected the boot flip-flop does not play any role and only the first set (Set #1) of memory maps are available. In either case the particular map within a set is selectable on J6.

The boot flip-flop is set after power-on reset or a push button reset. This is its main function -- to enable a PROM initially so that the PROM can load an operating system. The boot flip-flop can then be reset by an I/O operation. Refer to Table 3.5.

| TAB                                                                                                               | LE 3.5 BOOT FLIP FLOP                                           | CONTROL                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|--|--|

| OPERATION DESIRED                                                                                                 | DO THIS I/O<br>OPERATION                                        | RESULT IF J6                                                      |  |  |

| SET BOOT<br>FLIP-FLOP<br>RESET BOOT<br>FLIP-FLOP                                                                  | OUTPUT 0 TO PORT<br>F6H (See Note 2)<br>OUTPUT 1 TO PORT<br>F6H | MEMORY MAP SET #2 ENABLED MEMORY MAP SET #1 ENABLED (See Note #1) |  |  |

| Note 1: If only memory map set #1 is desired, connect J6 7&8 in which case the boot flip-flop effect is disabled. |                                                                 |                                                                   |  |  |

| Note 2:                                                                                                           | Boot flip-flop is al<br>of a power-on or pus                    | so set as a result                                                |  |  |

Memory map set \$1 contains 6 different memory maps that take care of various combinations of ROMS/PROMS/EPROMS and RAMS. Memory map set \$2, (intended to load an operating system into main memory) contains 2 different maps. The 2 memory map options of set \$2 are configured on J6 in such a way as to not have any identical configuration for set \$1 on J6. Thus if a map on set \$2 is selected there can only be an on-board memory operation if the boot flip-flop is on. Once it is turned off, set \$1 is enabled, as explained above, but the configuration on J6 does not select any map from this set.

Table 3.6 shows how to configure J6 for selecting the particular memory map. The table contains boxes showing memory size at each of the four sockets (U13 through U16). Also absolute location in the memory space is shown.

|              |                        | TABLE 3.6 ON BOARD MEMORY MAP SE                                                                   | SELECTION                                                                     |

|--------------|------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| <b>3</b> 10  | J6 PINS<br>1 THROUGH 6 | MEMORY MAP SET #1 SELECTED WHEN J6<br>7&8 CONNECTED OR J6 8&10 CONNECTED<br>BUT BOOT FLIP FLOP OFF | MEMORY MAP SET:#2 SELECTED WHEN<br>J6 8410 CONNECTED AND BOOT FLIP<br>FLOP ON |

| 0            | 162, 364, 556          |                                                                                                    | U13                                                                           |

| +            | 162, 364               |                                                                                                    | 4K 2K                                                                         |

| ~            | 162, 546               | U U U U<br>13 1445 16<br>2K 2K2K2K                                                                 |                                                                               |

| ~            | 1.6.2                  | U U<br>U13 U14 15 16<br>4K 4K 2K 2K                                                                |                                                                               |

| 4            | 354, 556               | 4K 4K 4K 4K                                                                                        |                                                                               |

| <u></u>      | 3 & 4                  | U13     U14     U       BK     2K2K                                                                |                                                                               |

| 9            | 5 & 6                  | H H H H H H H H H H H H H H H H H H H                                                              |                                                                               |

|              | NONE                   | и13 п14 и15 п16<br>8к вк вк                                                                        |                                                                               |

| <del>1</del> | ME' 'Y SPACE           | 0 4K 8K 12K 16K 20K 24 28K                                                                         | 0 4K BK 12K 16K 20K 34V 28K                                                   |

## 3.3 MEMEX AND ICEXP

## 3.3.1 <u>MEMEX</u>

Option posts E and F are connected when this card is to drive the MEMEX line. This card must drive the MEMEX line if there is an on-board accessible memory or if no other card in the system drives MEMEX.

## 3.3.2 <u>IOEXP</u>

Option posts D and C must normally be connected. It can be left open for the rare occasion that an external circuit would control this line.

## 3.4 ON-BOARD I/O

The on-board CTC (counter/timer controller) is used partly to provide the baud rate for the on-board serial I/O chip. (Channel zero of the CTC is dedicated for this purpose.) Refer to the programming section for further detail. Also refer to the programming section for the I/O addresses. The flip-flop is also an I/O addressable device; it is completely described in section 3.2.3.

## 3.4.1 <u>OUTPUT CONNECTORS</u>

Tables 3.7 and 3.8 show the pin assignments for the output connectors J2 and J3, used for the serial I/O and the timer/counter controller respectively.

### 3.4.2 <u>I/O CONFIGURATIONS</u>

The timer/counter controller can be configured on option post J4 to accept at its four CLK/TRG inputs one of six possible on-board sources. Three of the six sources are the CTC's own ZC/TO outputs so that the counters can be cascaded. Two of the sources are the 8251's (the serial chip) TXRDY and RXRDY signals for interrupt operation of the 8251. See section 2.6. The remaining source is the maximum frequency that the CTC can count -- 1/2 CPU clock. Table 3.9 provides the pin description of J4.

TABLE 3.7 OUTPUT CONNECTOR J2 - 14 pins (SERIAL I/O CONNECTOR)

| PIN   | SIGNAL | DESCRIPTION                 |

|-------|--------|-----------------------------|

| 1, 13 | GND    | For use as ground reference |

| 3     | TXD    | Transmitted Data see note   |

| 5     | RXD    | Received Data " "           |

| 7     | RTS    | Request-to-send " "         |

| 9     | CTS    | Clear-to-send " "           |

| 14    | DTR    | Data terminal ready " "     |

| All   | NC     | No connection               |

Note: This card is configured as DCE thus all signals are referenced to the opposite side (DTE).

| TABLE 3.8 OUTPUT CONNECTOR J3 - 16 pins (TIMER/COUNTER CONNECTOR) |                    |                                                      |  |  |

|-------------------------------------------------------------------|--------------------|------------------------------------------------------|--|--|

| PIN                                                               | SIGNAL             | DESCRIPTION                                          |  |  |

| !<br>  2<br>                                                      | <br>  CLK/TRG0<br> | Trigger or clock input to channel zero of CTC        |  |  |

| <br>  4<br>                                                       | CLK/TRG1           | Trigger or clock input to channel one of CTC         |  |  |

| 6                                                                 | CLK/TRG2           | Trigger or clock input to channel two of CTC         |  |  |

| !<br>!<br>!                                                       | CLK/TRG3           | Trigger or clock input to channel three of CTC       |  |  |

| 10                                                                | ZC/TO0             | Zero count or time-out output<br>channel zero of CTC |  |  |

| 12                                                                | 2C/T01             | Zero count or time-out output<br>channel one of CTC  |  |  |

| 14                                                                | ZC/TO2             | Zero count or time-out output<br>channel two of CTC  |  |  |

| 16                                                                | NC                 | No connection                                        |  |  |

| All<br>Odd<br>Pins                                                | GND                |                                                      |  |  |

| <br> <br>       | TABLE 3.9 CONFIGURATION OPTION POST J4                                           |                                                            |  |  |  |

|-----------------|----------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| J4<br>PIN       | SIGNAL                                                                           | DESCRIPTION                                                |  |  |  |

| 1               | CLK/TRG0                                                                         | Clock/trigger input of CTC channel 1                       |  |  |  |

| 2               | 1/2 CPU CLOCK                                                                    | 1.25 MHZ OR-2 MHZ FOR 2.5 MHZ or<br>4 MHZ CPU respectively |  |  |  |

| 3               | CLK/TRG1                                                                         | Clock/trigger input of CTC<br>Channel l                    |  |  |  |

| 4               | ZC/TOO                                                                           | Zero count/time-out of CTC<br>Channel 9                    |  |  |  |

| 5<br> <br>!     | CLK/TRG2                                                                         | Clock/trigger input of CTC<br>Channel 2                    |  |  |  |

| 6<br> <br>      | ZC/TO1                                                                           | Zero count/time-out of CTC<br>Channel 1                    |  |  |  |

| 7               | TXRDY                                                                            | Output of serial chip (8251)                               |  |  |  |

| <b>i 8</b><br>! | ZC/T02                                                                           | Zero count/time-out of CTC<br>Channel 2                    |  |  |  |

| 9               | RXRDY                                                                            | Output of serial chip (8251)                               |  |  |  |

| 10              | CLK/TRG3                                                                         | Clock/trigger of CTC Channel 3                             |  |  |  |

| Note            | Note: These signals are also available at the output connector J3. see table 3.8 |                                                            |  |  |  |

# 3.4.2.1 USING THE SERIAL CHIP

J4 pins 1 and 2 must be connected when using the serial chip since channel zero of the CTC provides its baud rate. J4 pin 4 is the output of channel zero. From here it is divided by two and made 50% duty cycle before reaching the serial chip.

Refer to Table 3.7 for the serial connector pin description. All the inputs and outputs are buffered by RS-232 buffers. The pins are conveniently positioned so that a cable with an RS-232 "D" connector at one end and a flat cable connector at the other can easily by made.

To use the serial chip inthe interrupt mode the signals RXRDY and TXRDY (J4 pins 9 and 7 respectively) are connected each to one of the three available CLK/TRG signals (J4 pins 3, 4, or 10). Also jumpers A and B must be connected. Refer to the programming section and Section 2.6.

# 3.4.2.2 <u>USING THE CTC TO CONTROL EXTERNAL INTERRUPTS</u>

The available CLK/TRG inputs of the CTC are connected via the output connector J3 to the interrupting source. Also jumpers A and B must be connected. It should be noted that these inputs are not buffered and go directly to the MOS inputs of the CTC. For further clarification refer to Section 2.6 and the programming section.

## 4.0 PROGRAMMING

This section provides I/O register addresses for the serial chip and the CTC, as well as guidelines to programming the CTC to provide the baud rate for the serial chip and interrupt control.

This section will not serve to instruct the user how to program the three LSI chips on-board. For this purpose the user should refer to the attached manufacturer's data sheets in appendices B, C, and E as well as other manufacturer publications.

Programming the boot flip-flop is not given here as it was more conveniently presented in Section 3.2.3.

## 4.1 <u>I/O ADDRESSES</u>

## 4.1.1 SERIAL CHIP ADDRESSES

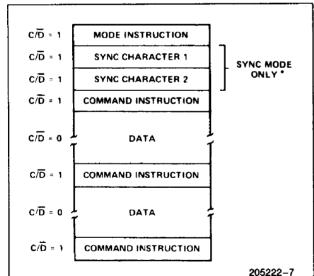

The serial chip has two addresses selected according to the C/D (Command/Data) input being '1' or '0'. Refer to Table 4.1.

| TABLE 4. | TABLE 4.1 - Serial Chip (8251)<br>Register Address |                |  |

|----------|----------------------------------------------------|----------------|--|

| ADDRESS  | C/D                                                | REGISTER       |  |

| F4       | 0                                                  | DATA           |  |

| F5       | 1                                                  | CONTROL/STATUS |  |

# 4.1.2 <u>CTC CHIP ADDRESSES</u>

The CTC has four addresses. Each address selects a different channel. Refer to Table 4.2

| TABLE 4.2 | CTC addresses |

|-----------|---------------|

| ADDRESS   | CHANNEL       |

| F0        | 0             |

| F1        | 1             |

| F2        | 2             |

| F3        | 3             |

# 4.2 SERIAL CHIP BAUD RATE PROGRAMMING

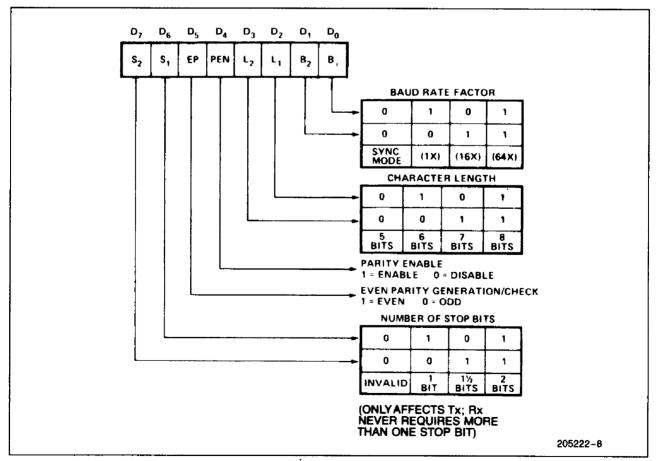

CHANNEL 0 of the CTC is used to generate the baud rate for the serial chip. All the standard asynchronous baud rates from 50 to 4800 can be programmed (except 50 baud for a 4MHZ CPU). Use Table 4.3 to determine the CTC time constant and the serial chip baud rate factor for a particular baud rate selection.

|                     | TABLE    | 4.3 BAUD      | RATE SELE              | CTION          |              |

|---------------------|----------|---------------|------------------------|----------------|--------------|

| <br>  BAUD RATE<br> | CTC CE   | HANNEL        | SERIAL<br>CHIP<br>BAUD | ACTUAL BA      | AUD RATE     |

| DESIRED             | 2.5 MHz  | 4 MHZ<br>CPU  | RATE<br>FACTOR         | 2.5 MHz<br>MHz | 4 MHz<br>CPU |

| <br>  50            | 195      | <br>  <b></b> | <br>  X64              | 50.08          |              |

| 110                 | i 89 i   | 142           | X64                    | 109.73         | 110.04       |

| 150                 | <br>  65 | 104           | X64                    | 150.24         | 150.24       |

| 300                 | 32       | 52            | X64                    | 305.18         | 300.48       |

| 600                 | 65       | 104           | X16                    | 600.96         | 600.96       |

| 1200                | 32       | 52            | X16                    | 1220.70        | 1201.92      |

| 2400                | 16       | 26            | X16                    | 2441.41        | 2403.85      |

| 4800                | 8        | 13            | X16                    | 4882.80        | 4807.69      |

| 9600                | 4        |               | X16<br>                | 9765.60        | <br>         |

### 4.2.1 GUIDELINES FOR BAUD RATE PROGRAMMING

The following two operations on the CTC set the baud rate:

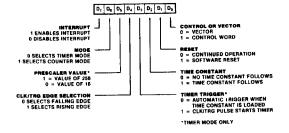

- (1) Output to port -- 01XXX111 disable interrupts/counter FO (channel 0) mode/time constant follows/reset/control word

- (2) Cutput to port

F0 (channel 0) -- TIME CONSTANT (From Table 4.3)

What still remains in order to set the baud rate is to program the serial chip for the desired baud rate factor (16x or 64x) according to Table 4.3.

#### 4.3 <u>USING THE CTC AS AN INTERRUPT CONTROLLER</u>

The CTC can be used as an interrupt controller for the serial chip and/or external events. See Section 3.4.2 for configurations. The following set of operations accomplishes this (for a particular channel).

- (1) Output to selected llx\*Xlll interrupt enable / counter mode / time constant follows / reset / control word

- (2) Output to selected -- 00000001 time constant of 1 channel

- (3) Output to channel VVVVV000 five significant bits O(F0)\*\*

- X Don't care

- \* In the case of the serial chip this should be 1. This will trigger an interrupt on the rising edge of a signal.

- \*\* Only one interrupt vector is used for all the channels and is loaded at channel 0.

For further clarification refer to Appendix D -- Manufacturer's Data sheet

#### 4.4 RESETTING THE SERIAL CHIP

For a safe reset of the serial chip always load the following sequence to port F5 (C/D=1) rather than just the reset command itself: 00H, 00H, 00H, and 40H. A software reset 40H on its own does not always work.

## APPENDICES

| A | ASSEMBLY, SCHEMATICS DIAGRAMS            |

|---|------------------------------------------|

| В | Z-80 DATA SHEET                          |

| С | SERIAL CHIP - 8251 - DATA SHEETS         |

| Þ | CTC (COUNTER/TIMER CHIP) DATA SHEETS     |

| E | MEMORY DECODER PROM                      |

| F | I/O DECODER PROM                         |

| G | PAL (PROGRAMMABLE LOGIC ARRAY) EQUATIONS |

#### APPENDICES

| A ASSEMBLY, SCHEMATICS DIA | AGRAMS |

|----------------------------|--------|

|----------------------------|--------|

- B Z-80 DATA SHEET

- C SERIAL CHIP 8251 DATA SHEETS

- D CTC (COUNTER/TIMER CHIP) DATA SHEETS

- E MEMORY DECODER PROM

- F I/O DECODER PROM

- G PAL (PROGRAMMABLE LOGIC ARRAY) EQUATIONS

#### **Product Specification**

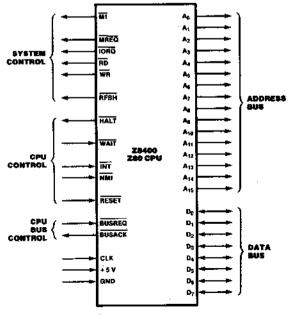

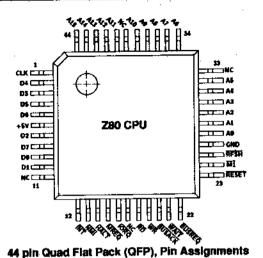

#### Z8400/Z84C00 NMOS/CMOS Z80° CPU Central Processing Unit

#### **FEATURES**

The extensive instruction set contains 158 instructions, including the 8080A instruction set as a subset.

- NMOS version for low cost high performance solutions, CMOS version for high performance low power designs.

- NMOS Z0840004 4 MHz, Z0840006 6.17 MHz, Z0840008 - 8 MHz.

- CMOS Z84C0006 DC to 6.17 MHz, Z84C008 DC to 8 MHz, Z84C0010 - DC to 10 MHz, Z84C0020 - DC -20 MHz

- 6 MHz version can be operated at 6.144 MHz clock.

- The Z80 microprocessors and associated family of peripherals can be finked by a vectored interrupt system. This system can be daisy-chained to allow implementation of a priority interrupt scheme.

- Duplicate set of both general-purpose and flag registers.

- Two sixteen-bit index registers.

- Three modes of maskable interrupts:

Mode 0—8080A similar;

Mode 1—Non-Z80 environment, location 38H;

Mode 2—Z80 family peripherals, vectored interrupts.

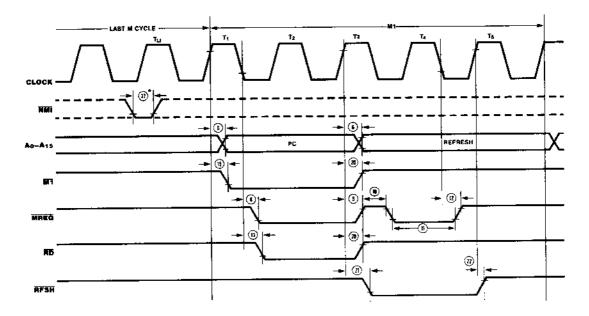

- On-chip dynamic memory refresh counter.

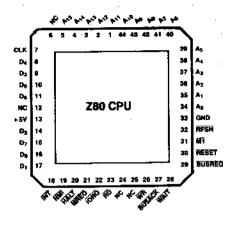

Figure 1. Pin Functions

Figure 2, 40-pln Dual-In-Line (DIP), Pin Assignments

Figure 2b. 44-Pin Chip Carrier Pin Assignments

#### GENERAL DESCRIPTION

The CPUs are fourth-generation enhanced microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second- and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response.

(Only available for 84C00)

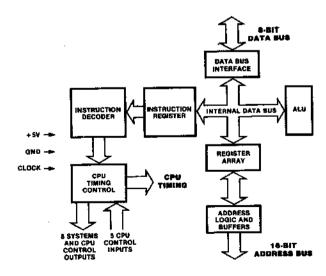

The CPU also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single +5V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits; the CPU is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the processors. Subsequent text provides more detail on the I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. Z80C CPU Block Diagram

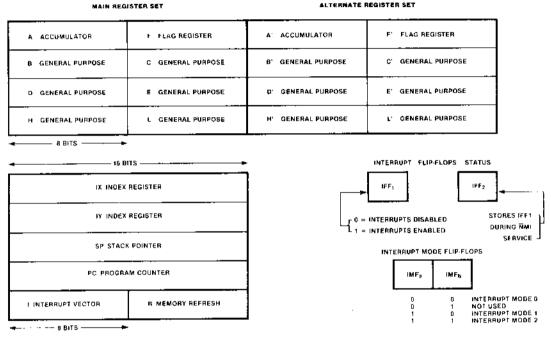

Table 1, Z80C CPU Registers

|           | Register           | Size (Blts) | Remarks                                                                                                                                                   |

|-----------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A, A'     | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                         |

| F, F'     | Flags              | 8           | See Instruction Set.                                                                                                                                      |

| B, B'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                    |

| C, C'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                    |

| D, D'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                                    |

| E, E'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                                    |

| H, H'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                                    |

| L, L'     | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                                    |

|           |                    | ·           | Note: The (B,C), (D,E), and (H,L) sets are combined as follows:  B — High byte — C — Low byte  D — High byte — E — Low byte  H — High byte — L — Low byte |

| I         | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                              |

| R         | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically incremented and placed on the address bus during each instruction fetch cycle.            |

| IX        | Index Register     | 16          | Used for indexed addressing.                                                                                                                              |

| IY        | Index Register     | 16          | Used for indexed addressing                                                                                                                               |

| SP        | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in instruction set.                                                                                |

| PC        | Program Counter    | 16 ·        | Holds address of next instruction.                                                                                                                        |

| FF1-IFF2  | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                                 |

| iMFa-IMFb | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                                    |

failure has been detected. After recognition of the NMI signal (providing BUSREQ is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

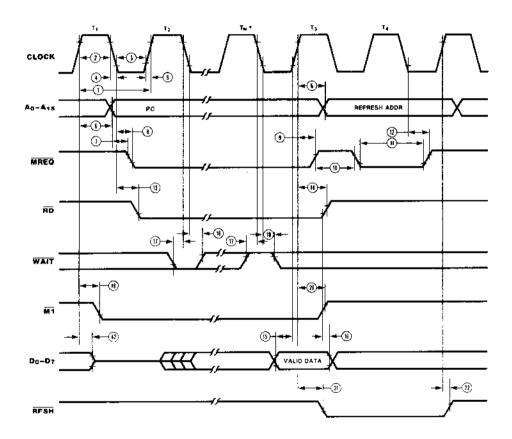

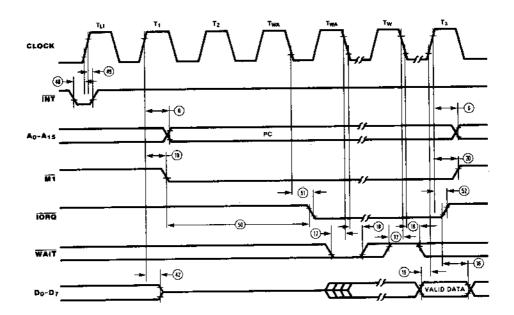

Maskable Interrupt (INT). Regardless of the interrupt mode set by the user, the CPU response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by the CPU (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (M1) cycle in which IORQ becomes active rather than MREQ, as in a normal M1 cycle. In addition, this special M1 cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request.

**Mode 0 Interrupt Operation.** This mode is similar to the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus. This is normally a Restart instruction, which will initiate a call

to the selected one of eight restart locations in page zero of memory. Unlike the 8080, the Z80 CPU responds to the Call instruction with only one interrupt acknowledge cycle followed by two memory read cycles.

**Mode 1 Interrupt Operation.** Mode 1 operation is very similar to that for the NMI. The principal difference is that the Mode 1 interrupt has only one restart location, 0038H.

Mode 2 Interrupt Operation. This interrupt mode has been designed to most effectively utilize the capabilities of the Z80 microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit vector on the data bus during the interrupt acknowledge cycle. The CPU forms a pointer using this byte as the lower 8 bits and the contents of the I register as the upper 8 bits. This points to an entry in a table of addresses for interrupt service routines. The CPU then jumps to the routine at that

address. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines. These routines may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0 (A.) must be a zero.

Interrupt Enable/Disable Operation. Two flip-flops, IFF1 and IFF2, referred to in the register description, are used to signal the CPU interrupt status. Operation of the two flip-flops is described in Table 2. For more details, refer to the Z80 CPU Technical Manual (03-0029-01) and Z80 Assembly Language Programming Manual (03-0002-01).

Table 2. State of File-Floors

| Action                       | tFF <sub>1</sub> | IFF <sub>2</sub> | Comments                                                                     |

|------------------------------|------------------|------------------|------------------------------------------------------------------------------|

| CPU Reset                    | 0                | 0                | Maskable interrupt                                                           |

| Ol instruction execution     | 0                | 0                | Maskable interrupt                                                           |

| El instruction execution     | 1                | 1                | Maskable interrupt<br>INT enabled                                            |

| LD At instruction execution  | •                | •                | IFF <sub>2</sub> → Parity flag                                               |

| LD A.R instruction execution | •                | •                | iFF <sub>2</sub> → Parity flag                                               |

| Accept NMI                   | 0                | •                | Maskable interrup<br>INT disabled                                            |

| RETN instruction execution   | IFF <sub>2</sub> | •                | IFF <sub>2</sub> → IFF <sub>1</sub> at completion of an NMI service routine. |

#### **INSTRUCTION SET**

The microprocessor has one of the most powerful and versatile instruction sets available in any 8-bit microprocessor. It includes such unique operations as a block move for fast, efficient data transfers within memory, or between memory and I/O. It also allows operations on any bit in any location in memory. The following is a summary of the instruction set which

shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. For an explanation of flag notations and symbols for mnemonic tables, see the Symbolic Notations section which follows these tables. The Z80 CPU Technical Manual (03-0029-01). the Programmer's Reference Guide (03-0012-03), and Assembly Language Programming Manual (03-0002-01) contain significantly more details for programming use.

The instructions are divided into the following categories:

□ 8-bit loads ☐ 16-bit loads Exchanges, block transfers, and searches 8-bit arithmetic and logic operations General-purpose arithmetic and CPU control 16-bit arithmetic operations

- Bit set, reset, and test operations

- Jumps

- Calls, returns, and restarts

- Input and output operations

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include:

- Immediate

- Immediate extended

- Modified page zero

- □ Relative

- Extended

- Indexed

- □ Register

- Register indirect

- □ Implied

- □ Bit

Rotates and shifts

#### 8-BIT LOAD GROUP

| Mnemonic       | Symbolic<br>Operation   |   | z |   | PM<br>H | gs | P/Y | N | c |    | Opcod<br>543 |     | Hear | No. of<br>Bytee | No. of M<br>Cycles | No. of T |       | ments |

|----------------|-------------------------|---|---|---|---------|----|-----|---|---|----|--------------|-----|------|-----------------|--------------------|----------|-------|-------|

| LD r, r'       | r =- r'                 | • | • | × | •       | х  | •   | • | • | 01 | г            | r'  |      | 1               | 1                  | 4        | r, r' | Reg.  |

| LD r, ri       | r≁n                     | • | • | х |         | Х  | •   | • | ٠ | 00 | r            | 110 |      | 2               | 2                  | 7        | 000   | В     |

|                |                         |   |   |   |         |    |     |   |   |    | <b>+</b> n→  | •   |      |                 |                    |          | 001   | C     |

| LD g (HL)      | r (HL)                  | • | • | X | ٠       | Х  | •   | • | • | 01 | r            | 110 |      | 1               | 2                  | 7        | 010   | D     |

| LDr. (IX+d)    | $r \leftarrow (1X + d)$ | • | ٠ | Х | •       | Х  | ٠   | ٠ | • | 11 | 011          | 101 | DD   | 3               | 5                  | 19       | 011   | E     |

|                |                         |   |   |   |         |    |     |   |   | 01 | r            | 110 |      | •               |                    |          | 100   | Н     |

|                |                         |   |   |   |         |    |     |   |   |    | +d→          | •   |      |                 |                    | •        | 101   | L     |

| LDr. (IY+d)    | r ← (IY + d)            | • | • | Х | •       | Х  | ٠   | • | ٠ | 11 | 111          | 101 | FD   | 3               | 5                  | 19 -     | 111   | A     |

|                |                         |   |   |   |         |    |     |   |   | 01 | Г            | 110 |      |                 |                    |          |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | q -          | ٠.  |      |                 |                    |          |       |       |

| LD (HL), r     | (HL) ← r                | • | • | Х | •       | Х  | •   | • | • | 01 | 110          | £   |      | 1               | 2                  | 7        |       |       |

| LD(IX+d), t    | 1 (D+XI)                | • | • | Х | •       | Х  | ٠   | ٠ | • | 11 | 011          | 101 | DĐ   | 3               | 5                  | 19       |       |       |

|                |                         |   |   |   |         |    |     |   |   | 01 | 110          | г   |      |                 |                    |          |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | <b>-</b> d-  |     | _    |                 | _                  |          |       |       |

| LD (IY+d), r   | (lY+d) ← r              | • | • | Х | •       | Х  | ٠   | • | • | 11 | 111          |     | FD   | 3               | 5                  | 19       |       |       |

|                |                         |   |   |   |         |    |     |   |   | 01 | 110          | г   |      |                 |                    |          |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | +-d⊣         |     |      | _               | _                  |          |       |       |

| LD (HL), n     | (HL) ← n                | • | • | Х | •       | Х  | •   | • | ٠ | 00 |              | 110 | 36   | 2               | 3                  | 10       |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | <b>←</b> n→  |     |      |                 | _                  |          |       |       |

| LD (IX + d), n | (iX+d) ← n              | • | • | X | •       | X  | •   | ٠ | ٠ | 11 | 011          | 101 | DD   | 4               | 5                  | 19       |       |       |

|                |                         |   |   |   |         |    |     |   |   | 00 |              | 110 | 36   |                 |                    |          |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | <b>←</b> d-  |     |      |                 |                    |          |       |       |

|                |                         |   |   |   |         |    |     |   |   |    | <b>-</b> n-  | •   |      |                 |                    |          |       |       |

#### 8-BIT LOAD GROUP (Continued)

|              | Symbolic              |   |   |   | Fla  | ge. |     |     |   |    | Opcod        | •   | •        | No. of | No. of M | No. of T |          |

|--------------|-----------------------|---|---|---|------|-----|-----|-----|---|----|--------------|-----|----------|--------|----------|----------|----------|

| Mnemonic     | Operation             | 8 | Z |   | Н    |     | PN  | N   | C |    | 543          |     | Hex      | Bytee  | Cycles   | States   | Comments |

| LD ( Y+d), n | (IY+d) <del>←</del> n | • | • | х | •    | х   | •   |     | • | 11 | 111          | 101 | FD       | 4      | 5        | 19       |          |

|              |                       |   |   |   |      |     |     |     |   | 00 | 110          | 110 | 36       |        |          |          |          |

|              |                       |   |   |   |      |     |     |     |   |    | <b>-</b> -d- | •   |          |        |          |          |          |

|              |                       |   |   |   |      |     |     |     |   |    | +-n →        | •   |          |        |          |          |          |

| D A, (BC)    | A ← (BC)              | • | ٠ | X | ., • | Х   | •   | •   | ٠ | 00 | 001          | 010 | 0A       | 1      | 2        | 7        |          |

| DA, (DE)     | A ← (DE)              | • | • | Х | • '  | Х   | •   | •   | • | 00 | 011          | 010 | 1A       | 1      | 2        | 7        |          |

| DA, (nn)     | A 🕶 (nn)              | • | • | Х | •    | Х   | ٠   | •   | ٠ | 00 | 111          | 010 | ЭА       | 3      | 4        | 13       |          |

|              |                       |   |   |   |      |     |     |     |   |    | <b>+</b> n→  | •   |          |        |          |          |          |

|              |                       |   |   |   |      |     |     |     |   |    | <b>+</b> -п- |     |          |        |          | _        |          |

| LD (BC), A   | (BC) ← A              | • | • | Х | •    | Х   | •   | •   | ٠ | 00 |              | 010 | 02       | 1      | 2        | 7        |          |

| LD (DE), A   | (DE) ← A              | • | • | Х | •    |     | •   | . • | • | 00 | 010          | 010 | 12       | 1      | 2        | 7        |          |

| LD (nn), A   | (nn) ← A              | • | • | Х | •    | Х   | •   | ٠   | • | 00 |              | 010 | 32       | 3      | 4        | 13       |          |

|              |                       |   |   |   |      |     |     |     |   |    | 4- N -       |     |          |        |          |          |          |

|              |                       |   |   |   | _    |     |     | _   |   |    | •- n         |     |          |        | •        |          |          |

| LD A, I      | A←I                   |   | # | Х | 0    | Х   | IFF | 0   | • | 11 | 101          | 101 | ED       | 2      | 2        | 9        |          |

|              |                       |   |   |   |      |     |     |     |   | 01 | 010          | 111 | 57       |        | 2        | 9        |          |

| LD A, FI     | A <del></del> FI      | # | : | Х | 0    | х   | IFF | O   | ٠ | 11 | 101          | 101 | ED       | 2      | 4        | •        |          |

|              |                       |   |   |   |      |     |     |     |   | 01 | 011          | 111 | 5F       |        | 2        | 9        |          |

| LD I, A      | I←A                   | • | • | Х | •    | Х   | •   | ٠   | • | 11 | 101          | 101 | ED       | 2      | 2        | 9        |          |

|              |                       |   |   |   |      |     |     |     | _ | 01 | 000          |     | 47<br>ED | 2      | 2        | 9        |          |

| LDR, A       | Ř←A                   | • | • | Х | •    | Х   | •   | •   | • | 11 | 101          | 101 | ED<br>4F | 2      | 2        | 3        |          |

|              |                       |   |   |   |      |     |     |     |   | 01 | 001          | 111 | 41       |        |          |          |          |

NOTE: 4FF, the content of the interrupt enable flip-flop, (IFF2), is copied into the P/V flag.

#### **16-BIT LOAD GROUP**

| Mnemonic    | Symbolic<br>Operation       | s | z |   | Fla |   |   | N | С |    | Opcode<br>543 |     | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Com | ments |

|-------------|-----------------------------|---|---|---|-----|---|---|---|---|----|---------------|-----|-----|-----------------|--------------------|--------------------|-----|-------|

| LD dd, nn   | dd ← nn                     | • | • |   | •   | х | • | • | • | 00 | dd0           | 001 |     | 3               | 3                  | 10                 | dd  | Pair  |

| 25 00,      |                             |   |   |   |     |   |   |   |   |    | <b>←</b> n→   |     |     |                 |                    |                    | 00  | BC    |

|             |                             |   |   |   |     |   |   |   |   |    | <b>←</b> n→   |     |     |                 |                    |                    | 01  | DE    |

| LD IX, nn   | IX + an                     | • | • | Х |     | х | • | • | • | 11 | 011           | 101 | DĐ  | 4               | 4                  | 14                 | 10  | HL    |

| ,           |                             |   |   |   |     |   |   |   |   | 00 | 100           | 001 | 21  |                 |                    |                    | 11  | SP    |

|             |                             |   |   |   |     |   |   |   |   |    | <b>←</b> n→   |     |     |                 |                    |                    |     |       |

|             |                             |   |   |   |     |   |   |   |   |    | ←n→           |     |     |                 |                    |                    |     |       |

| LD IY, nn   | JY ← πn                     | • | • | Х | •   | X | ٠ | • | ٠ | 11 | 111           | 101 | FD  | 4               | 4                  | 14                 |     |       |

|             |                             |   |   |   |     |   |   |   |   | 00 | 100           | 001 | 21  |                 |                    |                    |     |       |

|             |                             |   |   |   |     |   |   |   |   |    | <b>-</b> n→   | •   |     |                 |                    |                    |     |       |

|             |                             |   |   |   |     |   |   |   |   |    | <b>←</b> n →  | •   |     |                 |                    |                    |     |       |

| LD HL, (nn) | H + (nn + 1)                | ٠ | ٠ | X | •   | Х | • | • | • | 00 | 101           | 010 | 2A  | 3               | 5                  | 16                 |     |       |

|             | L 🛨 (nn)                    |   |   |   |     |   |   |   |   |    | ÷п→           |     |     |                 |                    |                    |     |       |

|             | •                           |   |   |   |     |   |   |   |   |    | <b></b> 11    |     |     |                 |                    |                    |     |       |

| LD đđ, (nn) | dd <sub>+1</sub> ← (nn + 1) | • | • | X | •   | Х | • | ٠ | • | 11 | 101           | 101 | ED  | 4               | 6                  | 20                 |     |       |

|             | dd <sub>L</sub> ← (nn)      |   |   |   |     |   |   |   |   | 01 | dd1           | 011 |     |                 |                    |                    |     |       |

|             |                             |   |   |   |     |   |   |   |   |    | <b>+</b> n→   | •   |     |                 |                    |                    |     |       |

|             |                             |   |   |   |     |   |   |   |   |    | <b>←</b> n →  | •   |     |                 |                    |                    |     |       |

NOTE:  $(PAiR)_H$ ,  $(PAiR)_L$  refer to high order and low order eight bits of the register pair respectively. e.g.,  $BC_L = C$ ,  $AF_H = A$ .

## 16-BIT LOAD GROUP (Continued)

| Mnemonic     | Symbolic<br>Operation                  | 8 | z |   | Fla<br>H |   | P/V | N | С |    | Opcod<br>543 |     | Hex  | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Соти | ments |

|--------------|----------------------------------------|---|---|---|----------|---|-----|---|---|----|--------------|-----|------|-----------------|--------------------|--------------------|------|-------|

| D (X, (nn)   | IX <sub>H</sub> ← (nn + 1)             | • |   | x |          | х | •   | • | • | 11 | 011          | 101 | DD   | 4               | 6                  | 20                 |      |       |

| D (34) (111) | !X <sub>L</sub> = (nn)                 |   |   |   |          |   |     |   |   | 00 | 101          | 010 | 2A   |                 |                    |                    |      |       |

|              | . , ,                                  |   |   |   |          |   |     |   |   |    | <b></b> n →  |     |      |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | <b>+</b> n → |     |      |                 |                    |                    |      |       |

| .D IY, (nn)  | (nn + 1)                               | • | • | Х | •        | X | •   | • | ٠ | 11 | 111          | 101 | FD   | 4               | 6                  | 20                 |      |       |

|              | IY <sub>L</sub> + (nn)                 |   |   |   |          |   |     |   |   | 00 | 101          | 010 | 2A : |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | <b></b> n →  | •   |      |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | <b>+</b> n → |     |      | _               | _                  |                    |      |       |

| .D (nn), HL  | (nn + 1) ← H                           | • | • | Х | •        | X | • . | • | ٠ | 00 | 100          |     | 22   | 3               | 5                  | 16                 |      |       |

|              | (nn) <del></del> L                     |   |   |   |          |   |     |   |   |    | +n→          |     |      |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | <b>←</b> n → |     |      |                 | •                  | ~~                 |      |       |

| LD (nn), dd  | (nn+1) ← dd <sub>H</sub>               | ٠ | • | X | ٠        | Х | •   | • | • | 11 |              | 101 | ED   | 4               | 6                  | 20                 |      |       |

|              | (nn) ← dd <sub>L</sub>                 |   |   |   |          |   |     |   |   | 01 |              | 011 |      |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | <b>←</b> n→  |     |      |                 |                    |                    |      |       |

|              |                                        |   |   | v | _        | U |     |   | _ |    | +- N →       |     | OD   | 4               | 6                  | 20                 |      |       |

| LD (nn), łX  | (nn + 1) ← IX <sub>H</sub>             | • | • | Х | •        | X | •   | • | • | 11 |              | 101 | 22   | 7               |                    | 20                 |      |       |

|              | (nn) ← IX <sub>L</sub>                 |   |   |   |          |   |     |   |   | 00 | +-n-         |     | 22   |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | -n-          |     |      |                 |                    |                    |      |       |

|              | ·                                      |   | _ | v | _        | v |     |   |   | 11 |              | 101 | FD   | 4               | 6                  | 20                 |      |       |

| LD (nn), IY  | (nn + 1) ← IY <sub>H</sub>             | • | • | ^ | •        | ^ | •   | • | • | 00 |              | 010 | 22   | 7               | •                  |                    |      |       |

|              | (nn) ← IYL                             |   |   |   |          |   |     |   |   | -  | +n-          |     |      |                 |                    |                    |      |       |

|              |                                        |   |   |   |          |   |     |   |   |    | +n-          |     |      |                 |                    |                    |      |       |

| LD SP, HL    | SP ← HL                                |   |   | x |          | х |     |   |   | 11 | 111          |     | F9   | 1               | 1                  | 6                  |      |       |

| LDSP, NE     | SP + IX                                |   |   | X | ٠        | × |     |   | • | 11 | 011          | 101 | DĐ   | 2               | 2                  | 10                 |      |       |

| LD 31, 1A    | 101 171                                |   |   |   |          | • |     |   |   | 11 | 111          | 001 | F9   |                 |                    |                    |      |       |

| LD SP, IY    | SP + IY                                |   |   | х |          | х |     | • |   | 11 | 111          | 101 | FD   | 2               | 2                  | 10                 |      |       |

| LD 01,11     | <b>.</b> , ,,                          |   |   |   |          |   |     |   |   | 11 | 111          | 001 | F9   |                 |                    |                    | gq   | Pair  |

| PU\$H qq     | (SP - 2) + qq <sub>L</sub>             | ٠ | ٠ | Х | •        | х | •   | • | • | 11 | qq0          | 101 |      | 1               | 3                  | 11                 | 00   | BC    |

|              | (SP~1) + qq <sub>H</sub>               |   |   |   |          |   |     |   |   |    |              |     |      |                 |                    |                    | 01   | DE    |

|              | SP SP -2                               |   |   |   |          |   |     |   |   |    |              |     |      |                 |                    |                    | 10   | HL    |

| PUSHIX       | (SP - 2) + IXL                         | • | • | Х | ٠        | X | •   | • | • | 11 | 011          | 101 | ÐD   | 2               | 4                  | 15                 | 11   | AF    |

|              | (SP-1) + IXH                           |   |   |   |          |   |     |   |   | 11 | 100          | 101 | £5   |                 |                    |                    |      |       |

|              | SP→SP-2                                |   |   |   |          |   |     |   |   |    |              |     |      |                 |                    |                    |      |       |

| PUSH IY      | (SP-2) - IYL                           | • | • | X | •        | × | •   | ٠ | • | 11 | 111          |     | FD   | 2               | 4                  | 15                 |      |       |

|              | (SP - 1) + IYH                         |   |   |   |          |   |     |   |   | 11 | 100          | 101 | E5   |                 |                    |                    |      |       |

|              | SP - SP - 2                            |   |   |   |          |   |     |   |   |    |              |     |      | _               | _                  |                    |      |       |

| POP qq       | qq <sub>H</sub> +- (SP + 1)            | • | • | Х | •        | X | •   | • | • | 11 | qq0          | 001 |      | 1               | 3                  | 10                 |      |       |

|              | qqL + (SP)                             |   |   |   |          |   |     |   |   |    |              |     |      |                 |                    |                    |      |       |

|              | SP→SP+2                                |   |   |   |          |   |     |   |   |    |              |     |      | •               |                    | - 14               |      |       |

| POP IX       | IX <sub>H</sub> <del>**</del> (SP + 1) | • | • | X | •        | X | •   | • | • | 11 |              |     |      | 2               | 4                  | 14                 |      |       |

|              | IX <sub>L</sub> ← (SP)                 |   |   |   |          |   |     |   |   | 11 | 100          | 001 | E1   |                 |                    |                    |      |       |

|              | SP → SP +2                             |   |   |   |          |   |     |   |   |    |              |     | -    | •               | 4                  | 14                 |      |       |

| POP IY       | IY <sub>H</sub> ← (SP + 1)             | • | • | Х | •        | X | . • | • | • | 11 |              |     |      | 2               | . *                | 1-4                |      |       |

|              | IY <sub>L</sub> ← (SP)                 |   |   |   |          |   |     |   |   | 11 | 100          | 001 | E1   |                 |                    |                    |      |       |

|              | SP - SP +2                             |   |   |   |          |   |     |   |   |    |              |     |      |                 |                    |                    |      |       |

NOTE:  $(PAIR)_H$ ,  $(PAIR)_L$  refer to high order and low order eight bits of the register pair respectively, e.g.,  $BC_L = C$ ,  $AF_H = A$ .

# EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS

| Mnemonic    | Symbolic<br>Operation                                               | 8 | z |   | FN: | ge | P/V      | N | ¢ | 76       | Opcod<br>543 | e<br>210   | Hex      | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Comments                                                                               |

|-------------|---------------------------------------------------------------------|---|---|---|-----|----|----------|---|---|----------|--------------|------------|----------|-----------------|--------------------|--------------------|----------------------------------------------------------------------------------------|

| EX DE, HL   | DE ++ HL                                                            | • | • | X | •   | x  | •        | • | • | 11       | 101          | 011        | EB       | 1               | 1                  | 4                  |                                                                                        |

| EX AF, AF'  | AF ** AF'                                                           | • | • | Х | ٠   | Х  | •        | • | ٠ | 00       | 001          | 000        | 08       | 1               | 1                  | 4                  |                                                                                        |

| EXX         | BC ++ BC'<br>DE ++ DE'<br>HL ++ HL'                                 | • | • | X | •   | X  | •        | • | • | 11       | 011          | 001        | D9       | 1               | 1                  | 4                  | Register bank<br>and auxiliary<br>register bank<br>exchange                            |

| EX (SP), HL | H ++ (SP + 1)<br>L ++ (SP)                                          | • | ٠ | X | •   | X  | ٠        | • | • | 11       | 100          | 011        | E3       | 1               | 5                  | 19                 |                                                                                        |

| EX (SP), IX | IX <sub>H</sub> ++ (SP+1)<br>IX <sub>L</sub> ++ (SP)                | • | • | X | ٠   | X  | •        | • | • | 11<br>11 | 011<br>100   | 101<br>011 | E3       | . 2             | 6                  | 23                 |                                                                                        |

| EX (SP), IY | IYH ++ (SP+1)                                                       | • | • | X | •   | X  | •        | • | • | 11       | 111          | 101        | FD       | 2               | 6                  | 23                 |                                                                                        |

|             | iYL •• (SP)                                                         |   |   |   |     |    | വ        |   |   | 11       | 100          | 011        | E3       |                 |                    |                    |                                                                                        |

| LOI         | (DE) ← (HL) DE ← DE + 1 HL ← HL + 1 BC ← BC ~ 1                     | • | • | X | 0   | X  | Ť        | 0 | • | 11<br>10 | 101<br>100   | 101<br>000 | ED<br>A0 | . 2             | 4                  | 16                 | Load (HL) into<br>(DE), increment<br>the pointers and<br>decrement the<br>byte counter |

|             |                                                                     |   |   |   |     |    | <b>②</b> |   |   |          |              |            |          |                 |                    |                    | (BC)                                                                                   |

| LDIR        | (DE) ← (HL) DE ← DE + 1 HL ← HL + 1 BC ← BC - 1 Repeat until BC = 0 | • | • | X | 0   | X  | 0        | 0 | • | 11<br>10 | 101<br>110   | 101<br>000 | ED<br>BO | 2 2             | 5<br>4             | 21<br>16           | ifBC≠0<br>IfBC ≠0                                                                      |

|             | •                                                                   |   |   |   |     |    | 0        |   |   |          |              |            |          |                 |                    |                    |                                                                                        |

| LDO         | (DE) + (HL) DE + DE - 1 HL + HL - 1 BC + BC - 1                     | • | • | X | 0   | X  | •        | 0 | • | 11<br>10 | 101<br>101   | 101<br>000 | ED<br>A8 | 2               | 4                  | 18                 |                                                                                        |

| LDDR        | (DE) ← (HL)                                                         |   |   | x | 0   | x  | @        | 0 |   | 11       | 101          | 101        | ED       | 2               | 5                  | 21                 | If BC ≠ 0                                                                              |

|             | DE + DE - 1 HL + HL - 1 BC + BC - 1 Repeat until BC = 0             |   | a |   |     |    | n        |   |   | 10       | 111          | 000        | 88       | 2               | 4                  | 16                 | If BC = 0                                                                              |

| CPI         | A (HL)<br>HL +- HL + 1<br>BC +- BC 1                                | * | * | × | ‡   | x  | <b></b>  | 1 | ٠ | 11<br>10 | 101<br>100   | 101<br>001 | ED<br>A1 | 2               | 4                  | 15                 |                                                                                        |

NOTE:

P/V flag is 0 if the result of BC - 1 = 0, otherwise P/V = 1.

P/V flag is 0 only at completion of instruction.

<sup>3</sup> Z flag is 1 if  $A = H_{\Sigma}$ , otherwise Z = 0.

# EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS (Continued)

|          | Symbolic     |   |          |   |          | ge |          |   | _ |       | Opcod |     |            | No. of      | No. of M |        | Comments                  |

|----------|--------------|---|----------|---|----------|----|----------|---|---|-------|-------|-----|------------|-------------|----------|--------|---------------------------|

| Mnemonic | Operation    | S | Z        |   | Н        |    | P/V      | N | C | 76    | 543   | 210 | Hex        | Bytes       | Cycles   | States | Comments                  |

|          |              |   | 3        |   |          |    | ①        |   |   |       |       |     |            |             |          |        |                           |

| CPIR     | A - (HL)     | ŧ | *        | X | <b>‡</b> | X  | ‡        | 1 | • | 11    | 101   | 101 | ED         | 2           | 5        | 21     | If BC ≠ 0 and<br>A ≠ (HL) |